# Analog Neuromorphic Module Based on Carbon Nanotube Synapses

Alex Ming Shen, Chia-Ling Chen, Kyunghyun Kim, Byungjin Cho, Andrew Tudor, and Yong Chen\*

Department of Mechanical and Aerospace Engineering, and California NanoSystems Institute, University of California, Los Angeles, California 90095, United States

**ABSTRACT** We report an analog neuromorphic module composed of p-type carbon nanotube (CNT) synapses and an integrate-and-fire (I&F) circuit. The CNT synapse has a field-effect transistor structure with a random CNT network as its channel and an aluminum oxide dielectric layer implanted with indium ions as its gate. A positive voltage pulse (spike) applied on the gate attracts electrons into the defect sites of the gate dielectric layer, and the trapped electrons are gradually released after the pulse is removed. The electrons modify the hole concentration and induce a dynamic postsynaptic current in the CNT channel. Multiple input spikes induce excitatory or inhibitory postsynaptic currents *via* excitatory or inhibitory CNT synapses, which flow toward an I&F circuit to trigger output spikes. The dynamic transfer function between the input and output spikes of the neuromorphic module is analyzed. The module could potentially be scaled up to emulate biological neural networks and their functions.

**KEYWORDS:** carbon nanotube • neuromorphic module • synapse • analog • spike

Requiring less power than a 100 W light bulb, the human brain can process large dimensional information such as images and speech much faster than a supercomputer.<sup>1,2</sup> The human brain contains  $\sim 10^{11}$  neurons working in parallel to process spike signals, which are millisecond-long potential pulses. A typical neuron receives spikes from a few thousand fellow neurons *via* synapses, which are the connections between two neurons. A spike triggers a dynamic analog postsynaptic current (PSC) in the neuron that lasts from a few milliseconds to seconds. The PSC is of two types: an excitatory postsynaptic current (EPSC) *via* an excitatory synapse increases the probability of triggering spikes in the postsynaptic neuron, and an inhibitory postsynaptic current (IPSC) *via* an inhibitory synapse decreases the probability of triggering spikes in the postsynaptic neuron. When the total PSC triggered by input spikes drives the neural potential above a threshold value, the neuron will “fire” output spikes; otherwise, it will remain silent.<sup>3,4</sup> While a computer relies on software to set its algorithms and perform calculations in a serial digit mode, a neural network processes signals in a parallel analog mode. The parallel analog mode of processing signals increases speed significantly and decreases energy consumption when processing large

dimensional information. Supercomputers have been used to imitate the complex nonlinear dynamic functions of a neural network. However, a supercomputer consumes much more energy and time than a neural network when the nonlinear dynamic algorithms of the neural network are implemented in the supercomputer by software.<sup>1–3</sup> Neural networks have also been emulated by large-scale Si neuromorphic circuits.<sup>5–7</sup> However, these circuits consumed substantially more energy than an equivalent neural network, and it is prohibitive to scale up the circuits to a size comparable with the biological neural network.<sup>2,8</sup> Recently the Hodgkin–Huxley axon has been emulated by a memristor-based circuit without transistor.<sup>9</sup> Synapses have also been emulated by electronic devices, such as floating gate silicon transistors,<sup>10</sup> nanoparticle organic transistors,<sup>11</sup> resistive switches,<sup>12,13</sup> memristors,<sup>14,15</sup> and carbon nanotube (CNT) transistors.<sup>4,16–18</sup> Most of the devices have successfully emulated the analog plasticity and memory functions of the synapses, but failed to emulate the dynamic analog EPSC and IPSC without a large scale peripheral Si circuit.<sup>5,9–13,15–17,19</sup> The power consumption for the synaptic devices to process a single spike ranged from  $\sim 1 \mu\text{W}/\text{spike}$  for the Si analog circuit,<sup>5</sup>  $\sim 2 \mu\text{W}/\text{spike}$  for the

\* Address correspondence to yongchen@seas.ucla.edu.

Received for review April 18, 2013 and accepted June 27, 2013.

Published online June 27, 2013

10.1021/nn401946s

© 2013 American Chemical Society

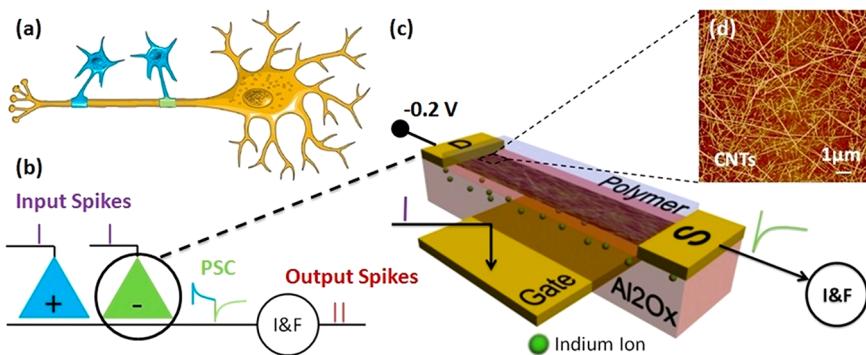

**Figure 1.** (a) A scheme showing a neuron (yellow) connected with two other neurons (blue) through synapses. (b) A scheme showing the structure of the neuromorphic module composed of an integrate-and-fire (I&F) axon circuit and synapses. Input spikes induce an excitatory postsynaptic current (EPSC) via an excitatory CNT synapse (blue “+” triangle) and an inhibitory postsynaptic current (IPSC) via an inhibitory CNT synapse (green “-” triangle). Dynamic postsynaptic currents (PSCs) flow jointly toward the I&F circuit and trigger output spikes via the I&F circuit. (c) A schematic of a CNT synapse with a channel composed of a random carbon nanotube (CNT) network connected with source (S) and drain (D) electrodes. Indium ions are implanted into an aluminum oxide dielectric layer in the transistor gate. A potential  $V_{ds} = -0.2$  V is applied on an inhibitory CNT synapse. An input spike applied on the transistor gate induces a dynamic current through the transistor channel as a PSC flowing from the transistor source toward the I&F circuit. (d) An atomic force microscope (AFM) image of a random CNT network in the transistor channel.

floating gate silicon transistor,<sup>20</sup>  $\sim 0.2 \mu\text{W}/\text{spike}$  for the resistive switch,<sup>19</sup> and  $\sim 50 \text{ nW}/\text{spike}$  for the nanoparticle organic transistors,<sup>11</sup> which are much higher than the power consumption of a biological synapse. In this work, we report an analog neuromorphic module to emulate the nonlinear dynamic functions of a neuron. The module is composed of CNT-based field-effect transistors to emulate synapses and a Si-based integrate-and-fire (I&F) circuit to emulate an axon. Input spikes can trigger dynamic analog EPSCs and IPSCs via excitatory and inhibitory CNT synapses with low power consumption ( $\sim 6 \text{ nW}/\text{spike}$ ). With its nanoscale diameter and superior electronic properties, CNT has been considered as a candidate to replace Si in nanoscale electronic circuits in the future. The EPSCs and IPSCs flow jointly toward an I&F circuit to trigger output spikes. A large-scale neuromorphic circuit based on the CNT synapses and Si transistors could potentially be scaled up to emulate biological neural networks with parallel signal processing and low energy consumption.

The neuromorphic module is designed to emulate a single neuron connected with other neurons through synapses (Figure 1a,b). The synapses are emulated by transistors based on a random CNT network (Figure 1c, d), and an axon in the neuron is emulated by a low-power I&F circuit based on Si transistors (Supporting Information).<sup>21</sup> As shown in Figure 1c, the transistor has an Al back gate and a 25-nm-thick  $\text{Al}_2\text{O}_3$  dielectric layer deposited by atomic layer deposition (ALD). By implanting indium ions into the  $\text{Al}_2\text{O}_3$  layer, defects were deliberately introduced into the dielectric layer. A network of single-wall p-type semiconducting CNTs was spin-coated onto the surface of the In-doped  $\text{Al}_2\text{O}_3$  layer and patterned to form a 15- $\mu\text{m}$ -wide and 20- $\mu\text{m}$ -long transistor channel, which was connected with Ti/Au source and drain electrodes. A positive voltage spike applied on the Al gate attracts electrons into the

$\text{Al}_2\text{O}_3$  dielectric layer, and the electrons are trapped locally near the defects in the  $\text{Al}_2\text{O}_3$  dielectric layer. After the spike is removed, the electrons are gradually released from the dielectric layer. The electrons trapped in the  $\text{Al}_2\text{O}_3$  dielectric layer increase the hole concentration in the p-type CNT, and hence the current in the CNT channel; after the spike, the hole concentration and the current relax back as electrons return from the dielectric layer to CNT, thus effecting a dynamic PSC through the CNT channel. When a positive source-drain voltage  $V_{ds} = 0.2$  V, is applied, a spike induces an EPSC, and the CNT transistor functions as an excitatory synapse; when a negative source-drain voltage  $V_{ds} = -0.2$  V, is applied, a spike induces an IPSC, and the CNT transistor functions as an inhibitory synapse. Multiple spikes with amplitude of 5 V and duration of 1 ms were applied on the gates of the multiple CNT synapses. The EPSCs and IPSCs through a set of excitatory and inhibitory synapses flow jointly toward the I&F circuit in parallel. The total PSC is amplified and integrated with respect to time by a capacitor in the I&F circuit (Supporting Information). A threshold current is set in the I&F circuit. When the total PSC is below the threshold, no output spike will be triggered; when the total PSC is increased above the threshold, an output spike is triggered, and the PSC integration starts over again from zero.<sup>21</sup> The spike rate increases nonlinearly with increasing PSC. The input spikes, PSC, and output spikes in the neuromorphic module can be measured by analog-to-digital converters (ADC). The details of the fabrication and measurement of the neuromorphic module are provided in the Methods section and Supporting Information.

## RESULTS AND DISCUSSION

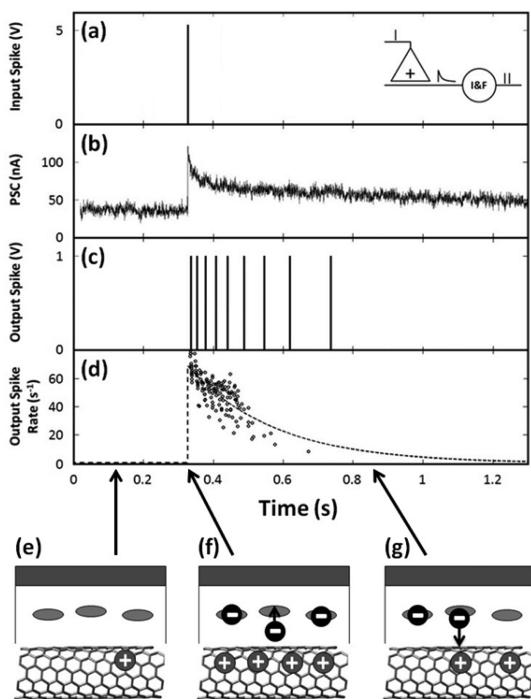

Figure 2 describes the operation of a typical excitatory CNT synapse inducing an EPSC. A single spike

**Figure 2.** (a) A single spike is input to a neuromorphic module *via* an excitatory CNT synapse. The inset schematic shows that an input spike induces an excitatory postsynaptic current (EPSC) and triggers a series of output spikes *via* an integrate-and-fire (I&F) circuit in the neuromorphic module. (b) The EPSC is shown *versus* time. (c) The series of output spikes is shown *versus* time. (d) The output spike rate (from 20 individual trials) is shown *versus* time, which is fitted by the dashed line. (e) A schematic showing hole ("+" circle) in the p-type CNT channel before an input spike is applied. (f) A schematic showing that the applied input spike attracts electrons ("—" circles) to the defects induced by the implanted In ions (gray ovals) in the  $\text{Al}_2\text{O}_3$  dielectric layer, increasing the hole concentration in the CNT channel. (g) A schematic showing that the electrons trapped in the dielectric layer gradually return to the CNT channel after the spike, reducing the hole concentration in the CNT channel.

(Figure 2a) is applied to the gate of the CNT synapse, inducing an EPSC (Figure 2b) with a peak amplitude of  $\sim 60$  nA above the resting current. It takes  $\sim 2$  s for the EPSC to gradually decay back to the resting current. The EPSC triggers a series of output spikes *via* the I&F circuit (Figure 2c). The firing rate of the output spikes decreases with the decreasing EPSC (Figure 2d). The output spikes end when the EPSC decays below the threshold value that is preset in the I&F circuit. For the case presented in Figure 2, this occurs at 0.8 s after the input spike is fired. The firing rate of the output spikes  $f(t)$  *versus* time  $t$ , from 20 individual trials can be fitted by the function  $f(t) = A \exp[-\alpha(t - t_0)]H(t - t_0)$ , where  $t_0$  represents the moment when the input spike is fired, and  $H(t)$  is a unit step function. From the best fit to the experimental data presented in Figure 2d, it was found that  $A = 70.2 \text{ s}^{-1}$  and  $\alpha = 4.1 \text{ s}^{-1}$ . When the EPSC is triggered by a spike, the CNT synapses are operated under a source-drain voltage  $V_{ds} = 0.2$  V and a gate voltage  $V_g = 5$  V. The gate current is  $< 10^{-12}$  A, and the power consumption induced by the gate

pulse and current can be neglected. An average EPSC (source-drain current) triggered by a single spike is  $\sim 30$  nA. The average power consumption of the CNT synapse is estimated to be  $0.2 \text{ V} \times 30 \text{ nA} = 6 \text{ nW/spike}$ .

We fabricated a reference device with the same structure as the CNT synapse, except that no In ions were implanted in the  $\text{Al}_2\text{O}_3$  dielectric layer. When a spike was applied on the gate of the control device, the source-drain current returned to its rest value immediately after the spike, and no obvious PSC was triggered by the spike (Supporting Information). The experimental results indicate that the PSC was related to the In ions implanted in the  $\text{Al}_2\text{O}_3$  dielectric layer. As we mentioned earlier, the PSC results from the dynamic response of a CNT synapse. As shown in Figure 2e–g, the input spike applied to the gate attracts electrons of the CNT to the defects associated with the In ions in the  $\text{Al}_2\text{O}_3$  dielectric layer. The negatively charged electrons in the dielectric layer attract positively charged holes in the p-type semiconducting CNTs in the channel, which increases the hole concentration in the CNT channel and the current through the CNT channel. After the spike, the electrons trapped in the dielectric layer gradually return to the CNT, leading to the gradual decrease of the hole concentration in the CNT channel and the decay of the current through the CNT channel. The PSC decay rate is determined by the speed for the electrons to leak out from the  $\text{Al}_2\text{O}_3$  dielectric layer, which in turn might be influenced by the thickness and defect density of the  $\text{Al}_2\text{O}_3$  dielectric layer.

The response of a neuron to temporally correlated signals can be tested by stimulating the neuron by a pair of input spikes with different time interval.<sup>22</sup> In our experiment, a pair of input spikes was applied to an excitatory CNT synapse to induce an EPSC and trigger output spikes in the neuromorphic module (Inset, Figure 3a). The time interval between the spike pair,  $\Delta t$ , varied between 1 and 40 ms. Figure 3a shows a spike pair with a time interval of 40 ms applied on an excitatory CNT synapse. The EPSC induced by the spike pair is shown in Figure 3b, and the output spikes triggered by the EPSC *via* the I&F circuit are shown in Figure 3c. The EPSC induced by the second input spike was superimposed on the EPSC induced by the first input spike. A shorter  $\Delta t$  results in a larger increase of the amplitude of the EPSC peak immediately after the second spike is applied (Figure S-4 in Supporting Information). This type of short-term correlation between the paired presynaptic spikes is called paired-pulse facilitation (PPF) in biological synapses.<sup>4</sup> The firing rate of the output spikes  $f(t)$ , *versus* time  $t$ , from 20 individual trials is shown in Figure 3d, which is fitted by the function  $f(t) = A_1 \exp[-\alpha_1(t - t_1)]H(t - t_1) + A_2 \exp[-\alpha_2(t - t_2)]H(t - t_2)$ , where  $t_1$  and  $t_2$  represent the times when the first input spike and second input spike are fired, respectively. From the best fit to the

**Figure 3.** (a) A pair of input spikes with a time interval of 40 ms applied on an excitatory CNT synapse. The inset shows schematically that a pair of spikes induces EPSC and triggers a series of output spikes *via* an I&F circuit in a neuromorphic module. (b) A PSC triggered by the input spike pair is shown *versus* time. (c) A series of output spikes triggered by the PSC *via* an I&F circuit is shown *versus* time. (d) The rate of output spikes (from 20 individual trials) is shown *versus* time, which is fitted by the dashed line.

experimental data (the dashed line in Figure 3d), it was found that  $A_1 = 23.5 \text{ s}^{-1}$ ,  $\alpha_1 = 0.92 \text{ s}^{-1}$ ,  $A_2 = 9.4 \text{ s}^{-1}$ , and  $\alpha_2 = 1.3 \text{ s}^{-1}$  when  $\Delta t = t_2 - t_1 = 40 \text{ ms}$ . The parameters  $A_1$  and  $\alpha_1$  are associated with the response of the neuromorphic module to the first input spike, which should not change against  $\Delta t$ . The parameters  $A_2$  and  $\alpha_2$  were derived from the best fit to the experimental data when  $\Delta t$  changed between 1 to 40 ms. As shown in Figure S-5 in the Supporting Information, when  $\Delta t$  increases from 1 to 40 ms, the parameter  $A_2$  gradually decreases from  $17.8 \text{ s}^{-1}$  to  $9.4 \text{ s}^{-1}$ , but the parameter  $\alpha_2$  fluctuates between  $0.77 \text{ s}^{-1}$  and  $20.9 \text{ s}^{-1}$  without an observable change trend against  $\Delta t$ .

The change of the parameter  $A_2$  against the  $\Delta t$  indicates that output spikes triggered by the pair of spikes are not simply the linear superposition of output spikes triggered by the two separated input spikes. The decrease of the parameter  $A_2$  with increasing  $\Delta t$  could be caused by the short-term memory of the CNT synapse. The first spike applied on the CNT synapse attracts the electrons into the  $\text{Al}_2\text{O}_3$  dielectric layer, and after the spike, the electrons are gradually released from the dielectric layer; when the second spike is applied, the electrons are partially released, and the residual electrons are injected into the defects located deeply in the dielectric layer. When the pair of spikes with a smaller time interval  $\Delta t$  are input to the CNT synapse, more electrons could be injected into the  $\text{Al}_2\text{O}_3$  dielectric layer, inducing more holes in the CNT channel and a larger EPSC.

The spatiotemporal temporal correlation between the input and output spikes in a neuron can be tested

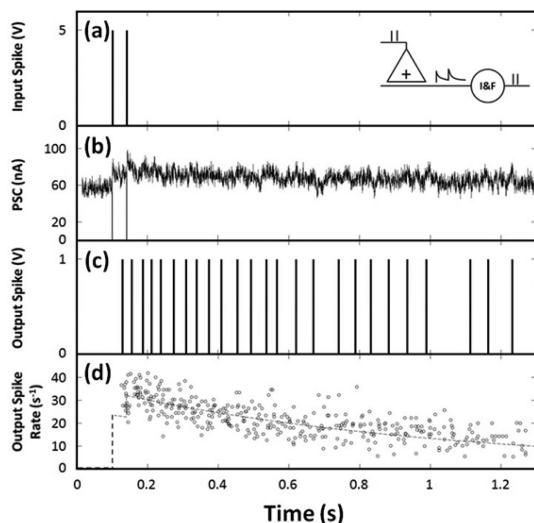

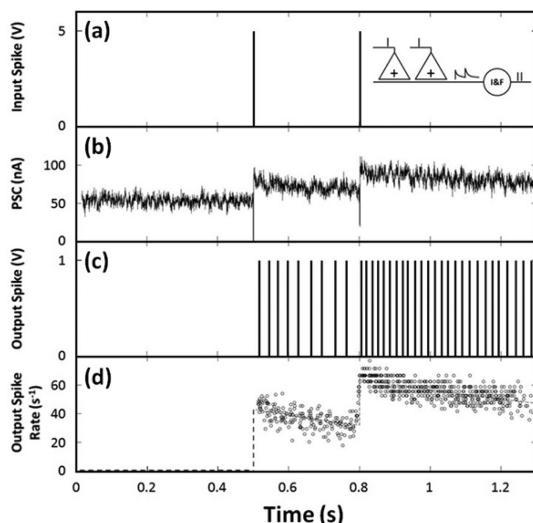

**Figure 4.** (a) A pair of input spikes with time interval of 300 ms applied separately on two excitatory CNT synapses. The inset shows schematically that two spikes are applied separately on two excitatory CNT synapses, induce EPSC, and trigger a series of output spikes *via* an I&F circuit in a neuromorphic module. (b) The PSC triggered by the input spike pair is shown *versus* time. (c) A series of output spikes triggered by the PSC *via* an I&F circuit is shown *versus* time. (d) The rate of output spikes (from 20 individual trials) is shown *versus* time, which is fitted by the dashed line.

by stimulating the neuron by a pair of spikes *via* different synapses. A pair of input spikes was applied to two excitatory CNT synapses separately to induce EPSCs and trigger output spikes in the neuromorphic module (inset, Figure 4a). Figure 4a shows two input spikes with a time interval of 300 ms applied separately on two excitatory CNT synapses. The EPSC induced by the spikes is shown in Figure 4b, and the output spikes triggered by the EPSC *via* the I&F circuit are shown in Figure 4c. The EPSC induced by the second spike was superimposed onto the EPSC induced by the first spike, increasing the rate of the output spikes. The firing rate of the output spikes  $f(t)$ , *versus* time  $t$ , from 20 individual trials is shown in Figure 4d. The  $f(t)$  is fitted by the function  $f(t) = A_1 \exp[-\alpha_1(t - t_1)]H(t - t_1) + A_2 \exp[-\alpha_2(t - t_2)]H(t - t_2)$ , where  $t_1$  and  $t_2$  represent the moments when the first input spike is on the CNT synapse 1 and the second input spike is on the CNT synapse 2, respectively. From the best fit to the experimental data (the dashed line in Figure 4d), it was found that  $A_1 = 43.0 \text{ s}^{-1}$  and  $\alpha_1 = 0.99 \text{ s}^{-1}$  for the CNT synapse 1, and that  $A_2 = 33.2 \text{ s}^{-1}$  and  $\alpha_2 = 0.29 \text{ s}^{-1}$  for the CNT synapse 2, when  $\Delta t = t_2 - t_1 = 300 \text{ ms}$ . The parameters  $A_1$  and  $\alpha_1$  are associated with the response of the neuromorphic module to the first input spike, which should not change against  $\Delta t$ . As shown in Figure S-6 in the Supporting Information, when  $\Delta t$  increases from 5 to 300 ms, the parameter  $A_2$  gradually increases from  $20.1 \text{ s}^{-1}$  to  $32.1 \text{ s}^{-1}$ , and parameter  $\alpha_2$  fluctuates between  $0.05 \text{ s}^{-1}$  and  $0.82 \text{ s}^{-1}$  without observable change trend against  $\Delta t$ .

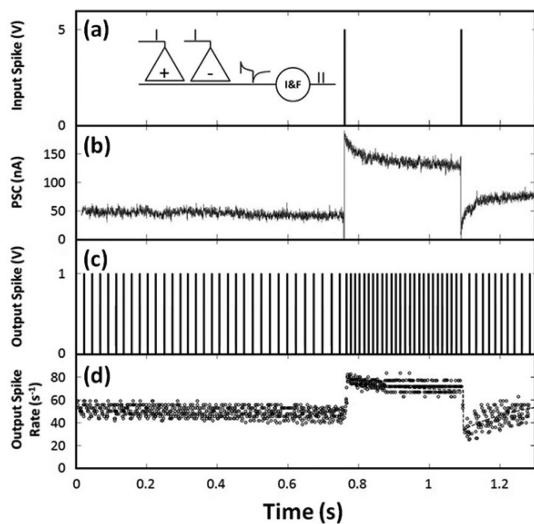

**Figure 5.** (a) A pair of input spikes with time interval of 328 ms applied separately on an excitatory CNT synapse and an inhibitory CNT synapse. The inset schematic shows that two spikes are applied separately on an excitatory CNT synapse and an inhibitory CNT synapse, induce an EPSC and an IPSC, and trigger a series of output spikes *via* an I&F circuit in a neuromorphic module. (b) The PSC triggered by the input spike pair is shown *versus* time. (c) A series of output spikes triggered by the PSC *via* an I&F circuit is shown *versus* time. (d) The rate of output spikes (from 20 individual trials) is shown *versus* time, which is fitted by the dashed line.

The change of the parameter  $A_2$  against the  $\Delta t$  indicates that output spikes triggered by the pair of spikes applied on the two excitatory synapses are not simply the linear superposition of output spikes triggered by the two separated input spikes. In this test only a single spike is applied on each CNT synapse, the nonlinear correlation between the input and output spikes is not the same as the synergistic effect of the spike pair on a single CNT synapse. The increase of the parameter  $A_2$  with increasing  $\Delta t$  could be caused by the nonlinear relation between the PSC and the output spike rate in the I&F circuit. It was observed in the I&F circuit that the output spike rate exhibited saturation behavior with increasing PSC. When  $\Delta t$  is small, a larger PSC appears after the second spike, resulting in a less increase of the output spike rate due to the nonlinear saturation of the I&F circuit.

A pair of input spikes was also applied separately to an excitatory CNT synapse and an inhibitory CNT synapse to induce EPSC and IPSC, and trigger output spikes in the neuromorphic module (inset, Figure 5a). Figure 5a shows two spikes applied separately on an excitatory CNT synapse and an inhibitory CNT synapse

with a time interval of 328 ms. The EPSC induced by the first spike and the IPSC induced by the second spike are shown in Figure 5b, and the output spikes triggered by the PSC *via* the I&F circuit are shown in Figure 5c. The first spike applied on the excitatory CNT synapse induced EPSC, resulting in the increase of the rate of the output spikes. The second spike applied on the inhibitory CNT synapse induced IPSC, resulting in the decrease of the rate of the output spikes. The firing rate of the output spikes  $f(t)$ , *versus* time  $t$ , from 20 individual trials is shown in Figure 5d. The  $f(t)$  is fitted by the function  $f(t) = A_1 \exp[-\alpha_1(t - t_1)]H(t - t_1) + A_2 \exp[-\alpha_2(t - t_2)]H(t - t_2)$ , where  $t_1$  represents the moment when the first input spike is applied on the excitatory CNT synapse, and  $t_2$  represents the moment when the second input spike is applied on the inhibitory CNT synapse. From the best fit to the experimental data (dashed line in Figure 5d), it was found that  $A_1 = 22.4 \text{ s}^{-1}$ ,  $A_2 = -33.4 \text{ s}^{-1}$ ,  $\alpha_1 = 0.18 \text{ s}^{-1}$ , and that  $\alpha_2 = 3.5 \text{ s}^{-1}$ . When  $\Delta t$  decreased from 328 to 100 ms, the best fit to the experimentally measured  $f(t)$  showed that  $A_2$  decreased from  $-33.4 \text{ s}^{-1}$  to  $-43.4 \text{ s}^{-1}$ , and  $\alpha_2$  decreased from  $3.5 \text{ s}^{-1}$  and  $2.4 \text{ s}^{-1}$ . As previously explained, the change of the parameter  $A_2$  could be induced by the nonlinear relation between the output spike rate and PSC in the I&F circuit.

## CONCLUSION

A nonlinear dynamic analog neuromorphic module composed of excitatory and inhibitory CNT synapses and a nonlinear integrate-and-fire (I&F) circuit was demonstrated. The channel of the CNT synapse was made from a random carbon nanotube (CNT) network, and indium ions were implanted into an aluminum oxide dielectric layer in its gate. A gate voltage pulse (spike) induces the dynamic change of the electron concentration attracted from the CNT and trapped in the gate dielectric layer, which in turn modifies the hole concentration in the CNT and induces a dynamic postsynaptic current (PSC) through the CNT channel. A spike applied on an excitatory CNT synapse with a positive source-drain voltage induces an excitatory PSC (EPSC). A spike applied on an inhibitory CNT synapse with a negative source-drain voltage induces an inhibitory PSC (IPSC). Multiple input spikes induce PSCs that jointly trigger output spikes *via* the I&F circuit. The nonlinear analog function of the neuromorphic module is analyzed. The module could potentially be scaled up to emulate biological neural networks with parallel signal processing with low energy consumption.

## METHODS

**Fabrication of CNT Synapse.** The back-gate of the CNT synapse was fabricated by depositing a 20-nm-thick titanium (Ti) and 80-nm-thick aluminum (Al) film onto a 300-nm-thick  $\text{SiO}_2$  layer

on a Si substrate using electron beam evaporation. A 20-nm-thick aluminum oxide ( $\text{Al}_2\text{O}_3$ ) dielectric layer was deposited *via* atomic layer deposition (ALD) and indium ions were implanted into the  $\text{Al}_2\text{O}_3$  layer with a concentration of  $3 \times 10^{18} \text{ atoms/cm}^3$

and an implantation energy of 5 keV. A 5-nm-thick  $\text{Al}_2\text{O}_3$  layer was then deposited onto the top of the ion-implanted  $\text{Al}_2\text{O}_3$  layer by ALD. After depositing a monolayer of (3-aminopropyl)-triethoxysilane (APTES) onto the surface of the  $\text{Al}_2\text{O}_3$  layer, a layer of random semiconducting single-wall CNTs was spin-coated onto the APTES-coated  $\text{Al}_2\text{O}_3$  surface. The CNT network was then patterned to make a 15- $\mu\text{m}$ -long, 20- $\mu\text{m}$ -wide CNT channel. The source and drain electrodes were fabricated by depositing 10-nm-thick Ti and 80-nm-thick Au films using electron beam evaporation. Finally, a 2- $\mu\text{m}$ -thick layer of SU-8 polymer was deposited and patterned to cap the CNT channel.

**Testing of Neuromorphic Module.** A source–drain voltage bias  $V_{ds} = 0.2$  V, was applied on the source electrode with respect to the drain electrode of the excitatory CNT synapse, and a source–drain voltage bias  $V_{ds} = -0.2$  V, was applied on the inhibitory CNT synapse. A constant idle voltage bias of 2 V was applied to the gate electrodes of the CNT synapse. Voltage spikes with duration of 1 ms and amplitude of 5 V were applied onto the gate electrodes of the CNT synapses. A field programmable gate array (FPGA) circuit was used to control and apply the spikes spatiotemporally onto the CNT synapses based on the test protocol. The spikes induced EPSCs and IPSCs, which collectively flowed toward the I&F circuit based on Si transistors. The total PSC was measured by the analog-to-digital converter (ADC). In the I&F circuit, an output spike was triggered when the integrated current reached a threshold value. After the spike was triggered, the I&F circuit was reset to start the integration over again. When the total PSC was increased, the frequency of the output spikes was increased.

**Conflict of Interest:** The authors declare no competing financial interest.

**Acknowledgment.** The authors acknowledge the support of this work by the Air Force Office of Scientific Research (AFOSR) under the program “Bio-inspired intelligent sensing materials for Fly-by-Feel autonomous vehicle” (Contract No. FA9550-09-1-0677). The authors also wish to acknowledge the support of A. Truong in the design of the device testing system.

**Supporting Information Available:** Description of the structure and fabrication process of a control device of the CNT synapse, the electrical characteristics of the CNT synapse and its control device, the measurement setup of the neuromorphic module, and paired-pulse testing results. This material is available free of charge via the Internet at <http://pubs.acs.org>.

## REFERENCES AND NOTES

1. Fischetti, M. Graphic Science: Computers vs. Brains. *Sci. Am. Mag.* **2011**, *305*, 104–104.

2. Watson, A. Why Can't a Computer be More Like a Brain? *Science* **1997**, *277*, 1934–1936.

3. Koch, C. Computation and the Single Neuron. *Nature* **1997**, *385*, 207–210.

4. Byrne, J.; Byrne, J. H.; Roberts, J. L., *From Molecules to Networks: An Introduction to Cellular and Molecular Neuroscience*; Academic Press: San Diego, CA, 2009; pg 470, 478, 544–545.

5. Indiveri, G.; Chicca, E.; Douglas, R. A VLSI Array of Low-Power Spiking Neurons and Bistable Synapses with Spike-Timing Dependent Plasticity. *IEEE Trans. Neural Network* **2006**, *17*, 211–221.

6. Arthur, J. V.; Boahen, K. A. Silicon-Neuron Design: A Dynamical Systems Approach. *IEEE Trans. Circuits Syst. I* **2011**, *58*, 1034–1043.

7. Mahowald, M.; Douglas, R. A Silicon Neuron. *Nature* **1991**, *354*, 515–518.

8. DiVincenzo, D. P. Toward Control of Large-Scale Quantum Computing. *Science* **2011**, *334*, 50–51.

9. Pickett, M. D.; Medeiros-Ribeiro, G.; Williams, R. S. A Scalable Neuristor Built with Mott Memristors. *Nat. Mater.* **2013**, *12*, 114–117.

10. Ramakrishnan, S.; Hasler, P. E.; Gordon, C. Floating Gate Synapses with Spike-Time-Dependent Plasticity. *IEEE Trans. Biomed. Circuits and Systems* **2011**, *5*, 244–252.

11. Alibart, F.; Pleutin, S.; Guérin, D.; Novembre, C.; Lenfant, S.; Lmimouni, K.; Gamrat, C.; Vuillaume, D. An Organic Nanoparticle Transistor Behaving as a Biological Spiking Synapse. *Adv. Funct. Mater.* **2010**, *20*, 330–337.

12. Kuzum, D.; Jeyasingh, R. G.; Lee, B.; Wong, H.-S. P. Nano-electronic Programmable Synapses Based on Phase Change Materials for Brain-Inspired Computing. *Nano Lett.* **2011**, *12*, 2179–2186.

13. Hasegawa, T.; Ohno, T.; Terabe, K.; Tsuruoka, T.; Nakayama, T.; Gimzewski, J. K.; Aono, M. Learning Abilities Achieved by a Single Solid-State Atomic Switch. *Adv. Mater.* **2010**, *22*, 1831–1834.

14. Park, H.; Afzali, A.; Han, S.-J.; Tulevski, G. S.; Franklin, A. D.; Tersoff, J.; Hannon, J. B.; Haensch, W. High-Density Integration of Carbon Nanotubes via Chemical Self-Assembly. *Nat. Nanotechnol.* **2012**, *7*, 787–791.

15. Erokhin, V.; Berzina, T.; Camorani, P.; Smerieri, A.; Vavoulis, D.; Feng, J.; Fontana, M. P. Material Memristive Device Circuits with Synaptic Plasticity: Learning and Memory. *J. Bionanosci.* **2011**, *1*, 24–30.

16. Kim, K.; Chen, C. L.; Truong, Q.; Shen, A. M.; Chen, Y. A Carbon Nanotube Synapse with Dynamic Logic and Learning. *Adv. Mater.* **2013**, *25*, 1693–1698.

17. Chen, C.; Kim, K.; Truong, Q.; Shen, A.; Li, Z.; Chen, Y. A Spiking Neuron Circuit Based on a Carbon Nanotube Transistor. *Nanotechnology* **2012**, *23*, 275202.

18. Joshi, J.; Zhang, J.; Wang, C.; Hsu, C.-C.; Parker, A. C.; Zhou, C.; Ravishankar, U. A Biomimetic Fabricated Carbon Nanotube Synapse for Prosthetic Applications. *IEEE LiSSA Workshop* **2011**, 139–142.

19. Nayak, A.; Ohno, T.; Tsuruoka, T.; Terabe, K.; Hasegawa, T.; Gimzewski, J. K.; Aono, M. Controlling the Synaptic Plasticity of a Cu2S Gap-Type Atomic Switch. *Adv. Funct. Mater.* **2012**, *22*, 3606–3613.

20. Chen, Y.; McDaid, L.; Hall, S.; Kelly, P. A Programmable Facilitating Synapse Device. *IEEE Int. Joint Conf. Neural Network* **2008**, 1615–1620.

21. Indiveri, G. A Low-Power Adaptive Integrate-and-Fire Neuron Circuit. *IEEE Int. Symp. Circuits Syst.* **2003**, *4*, IV-820–IV-823.

22. Debanne, D.; Guerineau, N. C.; Gähwiler, B.; Thompson, S. M. Paired-Pulse Facilitation and Depression at Unitary Synapses in Rat Hippocampus: Quantal Fluctuation Affects Subsequent Release. *J. Physiol.* **1996**, *491*, 163–176.